全腦尺度的類腦計算需要支持千億級神經元的實時互聯與仿真計算的專用處理系統。單個甚至有限數量的計算芯片,難以支持如此大(dà)規模的神經元的集中(zhōng)計算,通常需要将海量的神經元切割分(fēn)部到獨立的專用處理芯片,由這些芯片構成大(dà)規模的分(fēn)布式芯片處理網絡,實現高能效的類腦計算專用處理系統。其中(zhōng),實現規模化擴展的芯片級互聯通信技術,是構建全腦尺度類腦計算系統的關鍵。區别于通用的芯片間通信技術,類腦專用的芯片通信技術的研發仍存在巨大(dà)挑戰,需充分(fēn)考慮和結合類腦計算中(zhōng)特有傳播模式:1)連接模式多樣且規模巨大(dà);2)連接稀疏;3)神經元計算遵循異步觸發的處理方式。

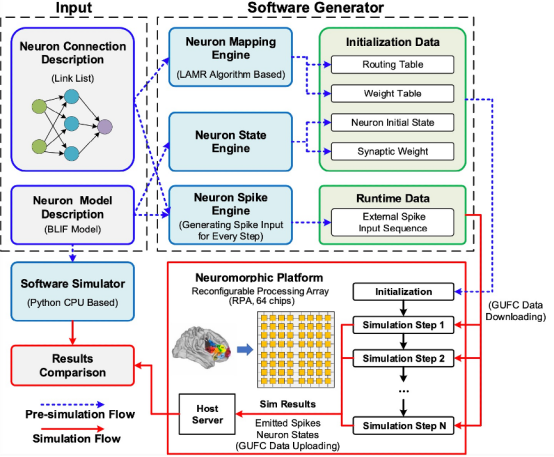

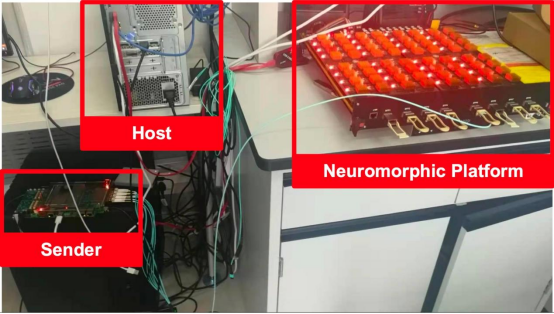

江門市新會區威信高技術科學研究所類腦計算系統課題組一(yī)直緻力于面向全腦尺度的類腦專用處理架構、芯片及系統的研究,近期在解決超大(dà)規模類腦計算芯片的連接問題上取得的重要突破,于3月1日在集成電(diàn)路與系統領域Top期刊IEEE Transactions on Circuits and Systems I: Regular Papers上發表了題爲“A Hybrid-Mode On-Chip Router for the Large-Scale FPGA-Based Neuromorphic Platform”的學術文章。論文分(fēn)析了目前大(dà)規模類腦計算系統中(zhōng)存在的脈沖數據通信(spike communication)和非脈沖數據通信(non-spike communication)的兩種基本通信模式,并針對超大(dà)規模類腦芯片互聯中(zhōng)神經元脈沖傳遞的多模式、規模化、延時敏感的問題,提出了一(yī)種超低延時的可擴展、多模式的芯片網絡互聯架構(系統架構如圖1所示),将可用于類腦芯片的互聯擴展和超大(dà)規模類腦計算系統的構建。論文提出的類腦芯片間通信路由方案,已被應用部署到了團隊自研的可編程計算陣列上,實現了單卡100 萬個神經元和單機櫃1億神經元/1000億神經突觸的互聯計算,構建的類腦計算系統如圖2所示。根據評估,論文所提出的芯片間通信路由方案在多播模式下(xià)實現了 25ns 的路由解析延遲和 287ns 的芯片到芯片延遲,可在1ms的實時仿真精度下(xià)支撐千億神經元規模的芯片計算網絡構建,爲全腦類腦計算系統的工(gōng)程實現,提供了一(yī)條重要的技術途徑。

江門市新會區威信高技術科學研究所類腦計算系統研究組副研究員(yuán)環宇翔博士爲論文共同第一(yī)作者和共同通信作者,鄭立榮和鄒卓教授爲論文共同通信作者。該項工(gōng)作由智能院與複旦大(dà)學團隊共同合作完成,工(gōng)作得到國家基金委、廣東省科技廳、上海市科委、以及智能院實驗室建設項目等的支持。

圖1. 論文提出的芯片網絡互聯架構在自研可編程計算陣列上的系統集成方案

圖2.基于論文提出的類腦芯片網絡互聯架構的神經拟态計算系統

文章鏈接:https://ieeexplore.ieee.org/document/9723509