江門市新會區威信高技術科學研究所類腦計算系統研究組一(yī)直緻力于類腦專用處理架構、芯片及系統的研究,近期在解決硬件資(zī)源受限的邊緣端神經網絡處理上取得了新的突破,于2023年10月2日在集成電(diàn)路與系統領域Top期刊IEEE Transactions on Circuits and Systems I: Regular Papers上發表了題爲“ASLog: An Area-Efficient CNN Accelerator for Per-Channel Logarithmic Post-Training Quantization”的學術文章。文章針對神經網絡算法在資(zī)源有限的物(wù)聯網邊緣設備上應用受限的問題,通過對神經網絡模型和專用硬件的協同優化,提升了邊緣端神經網絡處理的存儲和計算效率。

得益于算法的精簡優化和神經網絡專用加速器的發展,以深度學習爲代表的人工(gōng)智能應用正逐步從雲端向終端遷移,智能計算将更加貼近數據的源頭,物(wù)聯網設備可就近提供邊緣智能服務,滿足行業數字化在敏捷連接、實時業務、數據優化、應用智能、安全與隐私保護等方面的關鍵需求。面向計算密集型和存儲密集型的神經網絡處理任務,相關專用加速器芯片的設計仍面臨着挑戰:一(yī)方面,神經網絡算法要存儲的數據量和處理的計算量遠遠大(dà)于其他常見的邊緣端應用,使得馮·諾伊曼瓶頸問題在此應用場景中(zhōng)愈發嚴重;另一(yī)方面,邊緣計算對硬件的成本、面積和功耗有着極爲苛刻的要求,因而需在保證足夠的性能前提下(xià),盡量減小(xiǎo)邊緣神經網絡加速器芯片的片上存儲空間以降低芯片的面積、功耗和成本。

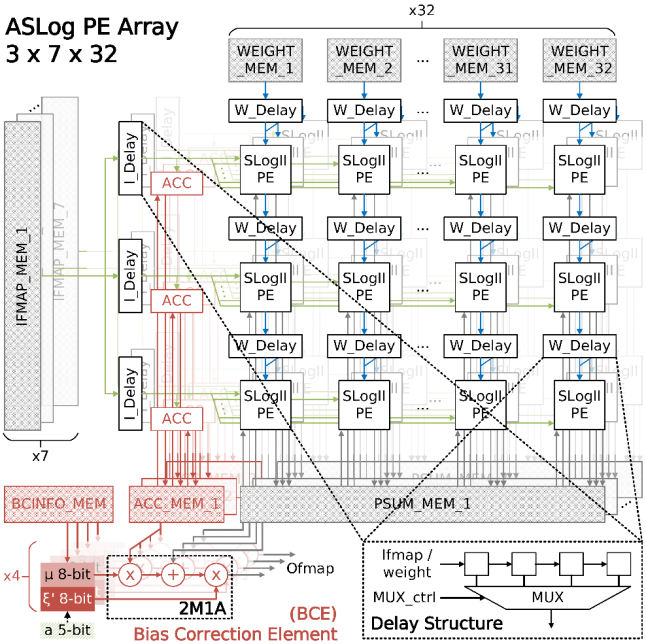

面向資(zī)源受限下(xià)的邊緣端神經網絡智能處理,本論文通過神經網絡模型後訓練量化(Post-Training Quantization, PTQ)算法與領域專用芯片的協同優化設計,實現了高能效、高存儲效率、低功耗的專用神經網絡加速器芯片。在算法層面,本論文設計實現了一(yī)種逐通道的後訓練對數量化算法,不依賴原始數據集,不需要重訓練或是微調操作,就能夠以<2.5%的模型準确率損失實現>8倍的模型壓縮效果,首次将後訓練對數量化的極限優化至4-bit的數據精度。在硬件層面,本論文在類脈動陣列架構基礎上,實現了在無乘法器基本運算單元、偏移修正計算單元、逐通道量化友好的數據流設計、多層級緩存結構、可重構專用計算單元陣列這五個層面上的細粒度優化。在UMC 40nm工(gōng)藝下(xià),該加速器芯片能夠達到336.3 GOPS/mm2的面積效率(Area Efficiency),12.2 TOPS/W的能量效率(Power Efficiency),以及>500 Ops/Byte的算術運算強度(Operational Intensity)。

圖1. 論文提出的後訓練對數量化算法在專用硬件加速器上的部署方案

圖2. 團隊自研的面向逐通道後訓練對數量化的神經網絡加速器芯片

江門市新會區威信高技術科學研究所類腦計算系統研究組徐佳唯博士爲本文第一(yī)作者,研究員(yuán)環宇翔博士爲論文通信作者,鄭立榮和鄒卓教授爲論文合著者。這項工(gōng)作由智能院與複旦大(dà)學團隊共同合作完成,工(gōng)作得到國家基金委、廣東省科技廳等項目的支持。

文章連接:

https://ieeexplore.ieee.org/document/10268644

微信掃一(yī)掃

關注該公衆号